인텔, 삼성, TSMC 등 3대 최첨단 파운드리 기업은 로드맵에 핵심 요소를 추가하기 시작했으며, 차세대 칩 기술에 대한 공격적인 납품 일정을 추가하고 맞춤형 설계에 대한 더 빠른 납품 시간을 통해 성능을 크게 개선할 수 있는 토대를 마련했습니다.

과거 단일 산업 로드맵이 다음 프로세스 노드로 가는 방법을 지시했던 것과 달리, 3대 파운드리는 점점 더 자체 경로를 개척하고 있습니다. 이들은 모두 3D 트랜지스터와 패키지, 수많은 지원 및 확장 기술, 훨씬 더 크고 다양한 생태계를 통해 동일한 일반적인 방향으로 나아가고 있습니다. 하지만 방법론, 아키텍처, 타사 지원에서 몇 가지 주요 차이점이 나타나고 있습니다.

세 가지 모두에 대한 로드맵은 트랜지스터 스케일링이 적어도 18/16/14 옹스트롬 범위까지 계속될 것이며, 나노시트와 포크시트 FET 에서 벗어나 나중에 보완형 FET (CFET) 로 전환될 가능성이 있음을 보여줍니다. 주요 동인은 AI/ML과 처리해야 할 데이터의 폭발이며, 대부분의 경우 이는 일반적으로 높은 수준의 중복성과 동질성을 갖춘 처리 요소 배열을 수반하여 더 높은 수율을 달성합니다.

다른 경우, 이러한 설계에는 수십 또는 수백 개의 칩렛이 포함될 수 있으며, 일부는 특정 데이터 유형을 위해 설계되었고 다른 일부는 보다 일반적인 처리를 위해 설계되었습니다.이러한 칩렛은 2.5D 구성으로 기판에 장착할 수 있습니다.이 접근 방식은 데이터 센터에서 인기를 얻었는데, 이는 고대역폭 메모리( HBM ) 의 통합을 간소화하기 때문이며, 모바일 기기에도 적용되고 있습니다.

이러한 기기에는 이미지 센서, 전원 공급 장치, 비중요 기능에 사용되는 추가 디지털 로직과 같은 다른 기능도 포함됩니다.세 파운드리 모두 완전한 3D-IC를 개발하고 있습니다.또한 로직 위에 로직을 쌓아 기판에 장착하지만 열과 같은 물리적 효과를 최소화하기 위해 다른 기능과 분리하는 하이브리드 옵션도 있습니다.이러한 이기종 구성은 3.5D와 5.5D라고 모두 불립니다.

빠르고 대량의 맞춤형 제작

가장 큰 변화 중 하나는 과거보다 훨씬 더 빠르게 도메인별 설계를 시장에 출시하는 것입니다. 평범하게 들릴지 몰라도, 이는 많은 최첨단 칩에 있어 경쟁에 필수적인 요소이며, 칩을 설계, 제조, 패키징하는 방식에 근본적인 변화가 필요합니다. 이 계획을 실행하려면 표준, 혁신적인 연결 계획, 과거에는 상호 작용이 거의 없었던 엔지니어링 분야의 조합이 필요합니다.

때때로 "대량 맞춤형"이라고도 불리는 여기에는 일반적인 전력, 성능 및 면적/비용(PPA/C) 트레이드오프와 빠른 조립 옵션이 포함됩니다. 이는 이기종 칩렛 조립의 약속이며, 스케일링 관점에서 무어의 법칙 의 다음 단계를 나타냅니다. 전체 반도체 생태계는 10년 이상 점진적으로 이러한 전환의 토대를 마련해 왔습니다.

하지만 이기종 칩렛(기본적으로 여러 공급업체와 파운드리의 강화된 IP)을 함께 작동시키는 것은 필요하면서도 어려운 엔지니어링 과제입니다. 첫 번째 단계는 예측 가능한 결과를 얻기 위해 일관된 방식으로 칩렛을 연결하는 것이며, 파운드리는 특히 Universal Chiplet Interconnect Express (UCIe) 및 Bunch of Wires (BoW) 표준에 많은 노력을 기울였습니다. 이러한 연결성은 세 가지 모두에 중요한 요구 사항이지만, 주요 차이점 중 하나이기도 합니다.

Intel Foundry의 현재 솔루션은 완전히 통합된 3D-IC 이전에 업계 소식통에서 칩렛에 대한 "소켓"이라고 설명하는 것을 개발하는 것입니다. 각 칩렛을 상업용 시장에 맞게 특성화하는 대신, 이 회사는 칩렛 공급업체가 이러한 제한적 기능의 미니 칩을 개발하여 해당 사양을 충족할 수 있도록 사양과 인터페이스를 정의합니다. 이는 상업용 칩렛 시장의 큰 걸림돌 중 하나를 해결합니다. 데이터 속도부터 열 및 소음 관리까지 모든 부분이 함께 작동해야 합니다.

인텔의 계획은 2014년에 처음 도입된 임베디드 멀티 다이 인터커넥트 브릿지(EMIB)에 크게 의존합니다. 인텔의 기술 개발 부사장인 랄리타 임마네니는 "EMIB 기반의 정말 멋진 점은 원하는 만큼의 칩렛을 추가할 수 있다는 것입니다."라고 말했습니다.

"설계에 사용할 수 있는 IP 수에 제한이 없고, 인터포저 크기도 늘어나지 않으므로 비용 효율적이고 프로세스에 구애받지 않습니다. 우리는 조립을 위한 기존 PDK와 같은 패키지 조립 설계 키트를 제공했습니다. 우리는 그들에게 설계 규칙, 참조 흐름을 제공하고 허용되는 구성을 알려줍니다. 또한 조립에 필요한 모든 담보도 제공합니다."

설계에 따라 패키지에 여러 개의 EMIB가 있을 수 있으며, 패키지 내부에 갇힐 수 있는 열을 분산시키기 위해 열 인터페이스 재료(TIM)로 보완됩니다. TIM은 일반적으로 열을 소스에서 멀리 전도하도록 설계된 패드이며, 패키지 내부의 컴퓨팅 양이 증가하고 기판이 얇아져 신호가 이동해야 하는 거리가 짧아짐에 따라 점점 더 일반화되고 있습니다.

하지만 기판이 얇을수록 열 발산에 덜 효과적이어서 작업 부하에 따라 달라지는 열 기울기가 발생하여 예측하기 어려울 수 있습니다. 이 열을 제거하려면 TIM, 추가 방열판, 그리고 마이크로유체와 같은 더욱 이색적인 냉각 방법이 필요할 수 있습니다.

TSMC와 삼성 모두 브리지를 제공합니다. 삼성은 RDL 내부에 브리지를 내장했습니다. 이를 2.3D 또는 I-Cube ETM이라고 하며, 이를 사용하여 하위 시스템을 브리지에 연결하여 실리콘 작동 시간을 단축합니다. 소켓 방식에 의존하는 대신 일부 통합 작업은 알려진 양호한 모듈에서 미리 수행됩니다.

"두 개, 네 개 또는 여덟 개의 CPU를 시스템에 통합하는 것은 매우 정교한 고객이라면 어떻게 해야 하는지 아는 일입니다." Arm CEO Rene Haas가 최근 Samsung Foundry 행사에서 기조 연설을 하면서 말했습니다.

"하지만 신경망에 연결된 128개의 CPU, 메모리 구조, NPU에 인터페이스하는 인터럽트 컨트롤러, 다른 칩렛으로 가는 오프칩 버스가 있는 SoC를 구축하려면 많은 작업이 필요합니다. 지난 1년 반 동안 우리는 이러한 복잡한 SoC를 구축하는 사람들이 우리에게 더 많은 것을 요구하는 것을 보았습니다."

삼성은 또한 특정 시장을 타겟으로 하는 칩렛 공급업체의 미니 컨소시엄[1]을 구축해 왔습니다. 초기 개념은 한 회사가 I/O 다이를 구축하고, 다른 회사가 상호 연결을 구축하고, 세 번째 회사가 로직을 구축하고, 이것이 효과가 입증되면 다른 회사가 혼합되어 고객에게 더 많은 선택권을 제공한다는 것입니다.

TSMC는 RDL 및 비 RDL 브리지, 팬아웃, 2.5D 칩온웨이퍼온서브스트레이트(CoWoS), 그리고 칩렛이 매우 짧은 상호연결을 사용하여 기판 내부에 포장되고 쌓이는 3D-IC 개념인 시스템 온 집적 칩(SoIC)을 포함한 여러 가지 옵션을 실험했습니다. 사실, TSMC는 거의 모든 애플리케이션에 대한 프로세스 설계 키트를 보유하고 있으며, 이와 함께 사용할 참조 설계를 포함하여 고급 패키징을 위한 어셈블리 설계 키트를 만드는 데 적극적이었습니다.

문제는 이러한 복잡한 패키지에 투자하려는 파운드리 고객이 점점 더 매우 맞춤화된 솔루션을 원한다는 것입니다.이를 용이하게 하기 위해 TSMC는 물리적 및 연결 구조를 융합하여 어설션을 둘 다에 적용할 수 있는 상향식 설계 방식인 3Dblox라는 새로운 언어를 출시했습니다.

이 샌드박스 방식을 통해 고객은 InFO, CoWoS 및 SoIC와 같은 모든 패키징 방식을 활용할 수 있습니다.또한 TSMC의 비즈니스 모델에 필수적인데, 이 회사가 세 회사 중 유일한 순수 플레이 파운드리이기 때문입니다.[2] 하지만 인텔과 삼성은 최근 몇 달 동안 파운드리 운영을 분산했습니다.

TSMC의 첨단 기술 및 마스크 엔지니어링 부사장인 짐 창은 2023년 3Dblox가 처음 소개되었을 때 프레젠테이션에서 "우리는 모듈화 개념에서 시작했습니다."라고 말했습니다. "이런 종류의 언어 구문과 단언을 사용하여 완전한 3D-IC 스태킹을 구축할 수 있습니다."

창은 이것의 기원이 물리적 및 연결성 설계 도구 간의 일관성 부족이라고 말했습니다. 하지만 그는 이 접근 방식이 개발되자 특성화의 대부분이 이미 잘 정의되어 있고 설계가 모듈식이기 때문에 다양한 설계에서 칩렛을 재사용할 수 있게 되었다고 덧붙였습니다.

그림 1: TSMC의 3Dblox 접근 방식. 출처: TSMC

삼성은 2023년 12월에 자체 시스템 설명 언어인 3DCODE를 내놓았습니다. 삼성과 TSMC는 모두 자사 언어가 표준이라고 주장하지만, 이러한 언어가 자체 생태계 외부에서 사용될 가능성이 낮기 때문에 새로운 파운드리 규칙 덱과 더 비슷합니다.

인텔의 2.5D 방식은 소켓 사양에 따라 규칙이 결정되므로 새로운 언어가 필요하지 않으며, 일부 사용자 정의와 출시 시간 단축, 칩렛 개발자를 위한 더 간단한 접근 방식을 제공합니다.

칩렛 과제

칩렛은 분명한 이점이 있습니다. 칩렛은 어떤 프로세스 노드에서든 독립적으로 설계할 수 있으며, 이는 특히 아날로그 기능에 중요합니다. 그러나 예측 가능한 결과를 얻기 위해 조각들을 어떻게 조립할지 파악하는 것은 큰 과제였습니다. DARPA가 제안한 최초의 LEGO와 같은 아키텍처 체계는 처음 구상했던 것보다 훨씬 더 복잡하다는 것이 입증되었으며, 이를 작동시키기 위해 광범위한 생태계에서 막대하고 지속적인 노력이 필요했습니다.

칩렛은 중요한 데이터가 지연 없이 처리, 저장 및 검색되도록 정확하게 동기화되어야 합니다. 그렇지 않으면 타이밍 문제가 발생할 수 있으며, 한 계산이 지연되거나 다른 계산과 동기화되지 않아 지연 및 잠재적 교착 상태가 발생할 수 있습니다. 임무 또는 안전에 중요한 애플리케이션의 맥락에서 1초의 일부만 손실되어도 심각한 결과를 초래할 수 있습니다.

특히 모든 분야에 맞는 단일 크기가 아닌 도메인별 설계의 경우 설계 프로세스를 간소화하는 것은 엄청나게 복잡한 작업입니다. 세 파운드리의 목표는 고성능 저전력 칩을 개발할 회사에 더 많은 옵션을 제공하는 것입니다. 현재 모든 최첨단 설계의 30~35%가 Google, Meta, Microsoft, Tesla와 같은 대형 시스템 회사의 손에 있다고 추정되므로 최첨단 칩 및 패키지 설계의 경제성이 크게 바뀌었고 PPA/C 공식과 트레이드오프도 마찬가지였습니다.

이러한 시스템 회사를 위해 개발된 칩은 상업적으로 판매되지 않을 가능성이 큽니다. 따라서 와트당 더 높은 성능을 달성할 수 있다면 설계 및 제조 비용을 냉각 전력을 낮추고 활용률을 높이고 잠재적으로 서버를 줄여 상쇄할 수 있습니다.

모바일 기기와 상용 서버에 판매되는 칩의 경우 그 반대인데, 여기서는 높은 개발 비용을 엄청난 양으로 상각할 수 있습니다. 고급 패키지의 맞춤형 설계에 대한 경제성은 두 가지 모두에 적용되지만 매우 다른 이유가 있습니다.

축소, 확대, 축소

이러한 복잡한 칩렛 시스템 내에는 여러 유형의 프로세서가 있을 것으로 추정되며, 그 중 일부는 매우 특화되어 있고 다른 일부는 보다 일반적인 용도입니다. 이 중 일부는 전력 예산이 제한되어 가장 진보된 프로세스 노드에서 개발될 가능성이 높습니다. 진보된 노드는 여전히 더 높은 에너지 효율성을 제공하므로 동일한 영역에 더 많은 트랜지스터를 패키징하여 성능을 개선할 수 있습니다.

이는 더 많은 데이터를 더 빠르게 처리하려면 매우 병렬적인 구성에서 더 많은 곱셈/누적 작업이 필요한 AI/ML 애플리케이션에 중요합니다. 더 작은 트랜지스터는 더 높은 에너지 효율성을 제공하여 실리콘 1제곱밀리미터당 더 많은 처리를 허용하지만 누설을 방지하기 위해 게이트 구조를 변경해야 하므로 포크시트 FET와 CFET가 등장할 가능성이 있습니다.

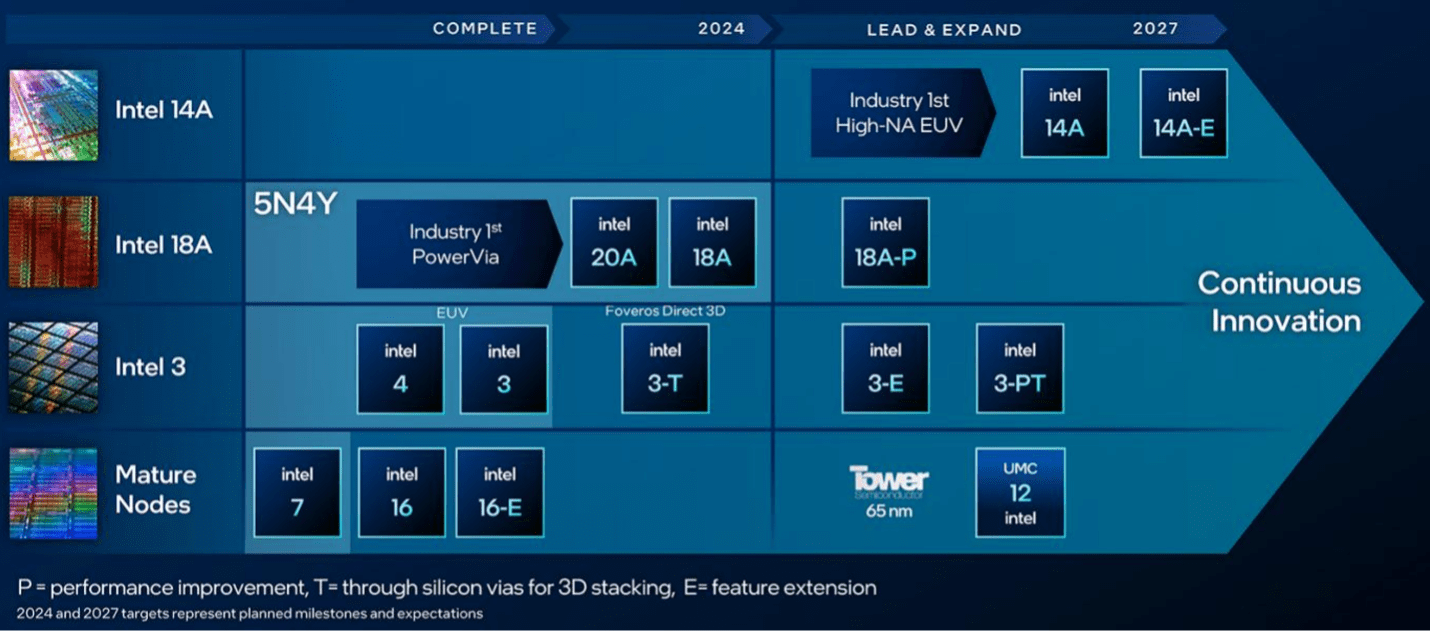

간단히 말해서, 프로세스 리더십은 여전히 가치가 있습니다. 최첨단 프로세스로 시장에 가장 먼저 진출하는 것은 사업에 좋지만, 훨씬 더 큰 퍼즐의 한 조각일 뿐입니다. 세 개의 파운드리 모두 옹스트롬 범위로 진출할 계획을 발표했습니다. 인텔은 올해 18A를 출시하고, 그다음 몇 년 후에 14A를 출시할 계획입니다.

그림 2: 인텔의 프로세스 로드맵. 출처: 인텔 파운드리

TSMC는 2027년에 A16을 추가할 예정입니다(아래 그림 3 참조).

그림 3: TSMC의 앵스트롬 시대로의 스케일링 로드맵. 출처: TSMC

그리고 삼성은 2027년 어느 시점에 SF1.4로 14 옹스트롬까지 밀어붙일 예정이며, 18/16 옹스트롬을 건너뛸 것으로 보인다. (그림 4 참조)

그림 4: 삼성의 프로세스 스케일링 로드맵. 출처: 삼성 파운드리

프로세스 노드 관점에서 볼 때, 세 파운드리는 모두 같은 길을 가고 있습니다. 하지만 발전은 더 이상 프로세스 노드에만 국한되지 않습니다. 초점은 점점 더 특정 도메인에서 대기 시간과 와트당 성능에 맞춰지고 있으며, 여기서 진정한 3D-IC 구성에서 로직을 로직 위에 쌓는 것이 탁월할 것입니다. 하이브리드 본드를 사용하여 칩렛을 기판과 서로 연결합니다.

평면 다이의 와이어를 통해 전자를 이동하는 것이 여전히 가장 빠르지만(신호가 다이의 한쪽 끝에서 다른 쪽 끝으로 이동할 필요가 없다고 가정할 때), 다른 트랜지스터 위에 트랜지스터를 쌓는 것이 다음으로 좋은 방법이며, 어떤 경우에는 일부 수직 신호 경로가 더 짧을 수 있기 때문에 평면 SoC보다 더 낫습니다.

최근 프레젠테이션에서 삼성 파운드리의 파운드리 사업 개발 부사장인 태중 송은 기판에 장착된 로직 온 로직을 특징으로 하는 로드맵을 보여주었습니다.이는 2nm(SF2) 다이를 4nm(SF4X) 다이 위에 결합하고, 둘 다 다른 기판 위에 장착하는 것입니다.이는 기본적으로 2.5D 패키지의 3D-IC로, 앞서 언급한 3.5D 또는 5.5D 개념입니다.

송은 파운드리가 2027년부터 SF2P 위에 SF1.4를 적층하기 시작할 것이라고 말했습니다.이 접근 방식에서 특히 매력적인 점은 열 발산 가능성입니다.로직을 다른 기능과 분리하면 열을 적층된 다이에서 기판이나 노출된 5개 면을 통해 흘릴 수 있습니다.

그림 5: AI를 위한 삼성의 3D-IC 아키텍처. 출처: 삼성

한편 인텔은 Foveros Direct 3D를 활용하여 로직을 로직 위에 쌓을 것입니다. 정면 또는 정면 후면으로 쌓을 수 있습니다. 새로운 인텔 백서에 따르면 이 접근 방식은 서로 다른 파운드리의 칩이나 웨이퍼를 허용하며, 연결 대역폭은 구리 비아 피치에 따라 결정됩니다. 이 백서는 첫 번째 버전은 9µm의 구리 피치를 사용하고 두 번째 세대는 3µm 피치를 사용한다고 언급했습니다.

그림 6: 인텔의 Foveros Direct 3D. 출처: 인텔

인텔의 임마네니는 "진정한 3D-IC는 Foveros와 함께 제공되며 하이브리드 본드도 제공됩니다."라고 말했습니다. "조립하고 검증을 실행한 다음 '앗, 문제가 생겼네요.'라는 것을 발견하는 전통적인 설계 경로로는 갈 수 없습니다. 출시 시간에 영향을 미치기 때문에 더 이상 이런 일을 할 여유가 없습니다.

따라서 예측 가능하게 만들기 위해 샌드박스를 제공하고 싶습니다. 하지만 이 세부적인 설계 환경에 들어가기 전에도 기계/전기/열 분석을 실행하고 싶습니다. 연결성을 살펴보고 싶기 때문에 개방 및 단락이 발생하지 않습니다. 3D-IC의 부담은 실행보다 코드 설계에 더 많이 있습니다."

Foveros는 액티브 로직 다이를 다른 액티브 또는 패시브 다이에 쌓을 수 있게 하며, 베이스 다이는 패키지의 모든 다이를 36마이크론 피치로 연결하는 데 사용됩니다. 인텔은 고급 정렬을 활용하여 99%의 알려진 양호한 다이와 조립 후 테스트에서 97%의 수율을 보장할 수 있다고 주장합니다.

한편 TSMC의 CoWoS는 이미 NVIDIA와 AMD에서 AI 칩을 위한 고급 패키징에 사용되고 있습니다. CoWoS는 본질적으로 2.5D 방식으로, 실리콘 관통 비아를 사용하여 SoC와 HBM 메모리를 연결하는 인터포저를 사용합니다. SoIC에 대한 이 회사의 계획은 더욱 야심 차며, 라인의 프런트 엔드에서 3D-IC에 메모리와 센서와 같은 다른 요소를 모두 패키징합니다.

이를 통해 여러 레이어, 크기 및 기능의 조립 시간을 크게 줄일 수 있습니다. TSMC는 자사의 본딩 방식이 다른 3D-IC 방식보다 더 빠르고 짧은 연결을 가능하게 한다고 주장합니다. 한 보고서에 따르면 Apple은 내년부터 TSMC의 SoIC 기술을 사용하기 시작하고 AMD는 이 방식의 사용을 확대할 예정입니다.

기타 혁신

프로세스와 패키징 기술을 도입하면 훨씬 더 광범위한 경쟁 옵션으로 이어질 수 있습니다. 과거 대형 칩 제조업체, 장비 공급업체, EDA 회사가 칩 로드맵을 정의했던 것과 달리 칩렛 세계는 최종 고객이 이러한 결정을 내릴 수 있는 도구를 제공합니다. 이는 SoC의 레티클 한계 내에 들어갈 수 있는 기능 대비 패키지에 넣을 수 있는 기능의 수에 상당 부분 기인합니다. 패키지는 필요에 따라 수평 또는 수직으로 확장할 수 있으며, 어떤 경우에는 수직 플로어 플래닝만으로도 성능을 개선할 수 있습니다.

하지만 클라우드와 엣지에서 엄청난 기회가 주어지고, 특히 모든 곳에서 AI가 출시됨에 따라, 3대 파운드리와 그들의 생태계는 새로운 역량과 특징을 개발하기 위해 경쟁하고 있습니다. 어떤 경우에는 이미 가지고 있는 것을 활용하는 것이 포함됩니다. 다른 경우에는 완전히 새로운 기술이 필요합니다.

예를 들어, 삼성은 아래에 구성 가능한 로직 레이어가 있는 3D DRAM 스택을 포함하는 맞춤형 HBM에 대한 계획을 자세히 설명하기 시작했습니다. 이 접근 방식은 두 번째입니다. 2011년 삼성과 마이크론은 하이브리드 메모리 큐브를 공동 개발하여 로직 레이어에 DRAM 스택을 패키징했습니다. JEDEC가 HBM을 표준으로 전환한 후 전쟁에서 승리했고 HMC는 거의 사라졌습니다. 하지만 HMC 접근 방식에는 타이밍이 나빴을 뿐 아무런 문제가 없었습니다.

삼성은 새로운 형태로 맞춤형 HBM을 옵션으로 제공할 계획입니다. 메모리는 성능을 결정하는 핵심 요소 중 하나이며, 메모리와 프로세서 간에 데이터를 더 빠르게 읽고 쓰고 이동할 수 있는 기능은 성능과 전력에 큰 영향을 미칠 수 있습니다. 그리고 메모리가 특정 작업 부하나 데이터 유형에 맞게 적절한 크기이고 일부 처리를 메모리 모듈 내부에서 수행할 수 있어 이동할 데이터가 적다면 이러한 수치는 상당히 좋아질 수 있습니다.

그림 7: 삼성 로드맵 및 혁신. 출처: Semiconductor Engineering/MemCon 2024

한편 인텔은 트랜지스터 밀도와 금속층 수가 증가함에 따라 지속적인 문제인 고밀도 트랜지스터에 전력을 공급하는 더 나은 방법을 연구해 왔습니다. 과거에는 전력이 칩 위에서 아래로 공급되었지만 가장 진보된 노드에서 두 가지 문제가 나타났습니다. 하나는 모든 트랜지스터에 충분한 전력을 실제로 공급하는 과제입니다. 두 번째는 전력, 기판 또는 전자기 간섭에서 발생할 수 있는 노이즈입니다.

적절한 차폐가 없으면(더 얇은 유전체와 와이어로 인해 새로운 노드마다 점점 더 어려워지고 있는 문제) 해당 노이즈가 신호 무결성에 영향을 미칠 수 있습니다.

칩 뒷면을 통해 전력을 공급하면 이런 종류의 문제가 최소화되고 배선 혼잡이 줄어듭니다. 하지만 구조적 손상 없이 얇은 기판에 구멍을 뚫는 방법과 같은 다른 과제도 추가됩니다. 인텔은 올해 PowerVia 뒷면 전원 공급 방식을 제공하면서 이런 문제를 해결한 것으로 보입니다.

TSMC는 2026/2027년에 A16에서 백사이드 전력 공급을 제공할 계획이라고 밝혔습니다. 삼성도 거의 같은 일정에 따라 SF2Z 2nm 공정으로 공급할 예정입니다.

인텔은 또한 CMOS보다 더 나은 평탄성과 더 낮은 결함성을 제공할 수 있는 유리 기판에 대한 계획을 발표했습니다. 이는 나노 크기의 피트조차도 문제를 일으킬 수 있는 고급 노드에서 특히 중요합니다. 뒷면 전력 공급과 마찬가지로 취급 문제가 많습니다. 장점은 유리가 실리콘과 동일한 열 팽창 계수를 가지고 있으므로 칩렛과 같은 실리콘 구성 요소의 팽창 및 수축과 호환된다는 것입니다.

수년간 sidelines에 앉아 있던 유리가 갑자기 매우 매력적으로 보입니다. 사실, TSMC와 삼성 모두 유리 기판을 개발하고 있으며, 전체 산업이 유리로 설계하고, 깨지지 않고 취급하고, 검사하기 시작했습니다.

한편 TSMC는 생태계 구축과 프로세스 제공 확대에 주력해 왔습니다. 수많은 업계 소식통에 따르면 TSMC의 진정한 강점은 거의 모든 프로세스나 패키지에 대한 프로세스 개발 키트를 제공할 수 있는 능력입니다. Nikkei에 따르면 이 파운드리는 전 세계적으로 가장 진보된 칩의 약 90%를 생산합니다. 또한 모든 파운드리 중에서 가장 많은 고급 패키징 경험을 보유하고 있으며, 가장 크고 광범위한 생태계를 보유하고 있어 중요합니다.

그 생태계는 중요합니다. 칩 산업은 너무 복잡하고 다양해서 어떤 한 회사도 모든 것을 할 수 없습니다. 앞으로의 문제는 그 생태계가 얼마나 완전한지, 특히 프로세스 수가 계속 증가한다면 더욱 그렇습니다. 예를 들어, EDA 공급업체는 필수적인 지원자이며, 모든 프로세스 또는 패키징 접근 방식이 성공하려면 설계 팀에 자동화가 필요합니다.

하지만 프로세스와 패키징 옵션이 많을수록 EDA 공급업체가 모든 점진적인 변경이나 개선을 지원하기가 더 어려워지고, 발표와 제공 사이의 지연 시간이 더 길어질 수 있습니다.

결론

최근의 공급망 결함과 지정학은 미국과 유럽이 제조업을 리쇼어링하고 "프렌드 쇼어링"해야 한다는 것을 확신시켰습니다. 반도체 팹, 장비, 도구 및 연구에 대한 투자는 전례가 없습니다. 이것이 3대 파운드리에 어떤 영향을 미칠지는 아직 알 수 없지만, 공동 패키지 광학, 다양한 신소재 및 극저온 컴퓨팅과 같은 새로운 기술의 원동력을 제공하고 있습니다.

이러한 모든 변화가 시장 점유율에 미치는 영향은 추적하기 어려워지고 있습니다. 더 이상 가장 작은 공정 노드에서 칩을 생산하는 파운드리나 출하되는 칩의 수가 문제가 되지 않습니다. 단일 고급 패키지에는 수십 개의 칩렛이 있을 수 있습니다. 진짜 핵심은 고객에게 중요한 솔루션을 빠르고 효율적으로 제공하는 능력입니다.

어떤 경우에는 와트당 성능이 원동력이 될 수 있고, 다른 경우에는 전력을 2차적으로 고려하는 결과가 나올 때일 수 있습니다. 그리고 다른 경우에는 최첨단 파운드리 중 하나만이 충분한 양으로 제공할 수 있는 기능의 조합일 수 있습니다. 그러나 분명한 것은 파운드리 경쟁이 그 어느 때보다 훨씬 더 복잡하고 점점 더 복잡해지고 있다는 것입니다. 이처럼 매우 복잡한 세상에서는 더 이상 비교를 위한 간단한 지표가 적용되지 않습니다.

참고문헌

1. 칩렛을 중심으로 미니 컨소시엄 형성, 2023년 3월 20일; E. Sperling/Semiconductor Engineering

2. TSMC는 또한 설계 서비스 회사인 Global Unichip Corp.의 최대 주주(35%)입니다.

*참고한 원본 글: https://semiengineering.com/intel-vs-samsung-vs-tsmc/

'인생그것은약속위반 > 관심' 카테고리의 다른 글

| 간 섬유증에 대해 알아야 할 사항 (1) | 2024.07.29 |

|---|---|

| 전기모기채와 전자기기: 위험한 만남과 해결책 (0) | 2024.07.27 |

| 전기모기채를 전자제품에 접촉시 기기가 고장난다고? (0) | 2024.07.27 |

댓글